在高速 PCB 设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应如何分配?

一般在空白区域的敷铜绝大部分情况是接地。 只是在高速信号线旁敷铜时要注意敷铜与信号线的距离, 因为所敷的铜会降低一点走线的特性阻抗。也要注意不要影响到它层的特性阻抗。

在高速设计中,如何解决信号的完整性问题?

信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(outputimpedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。

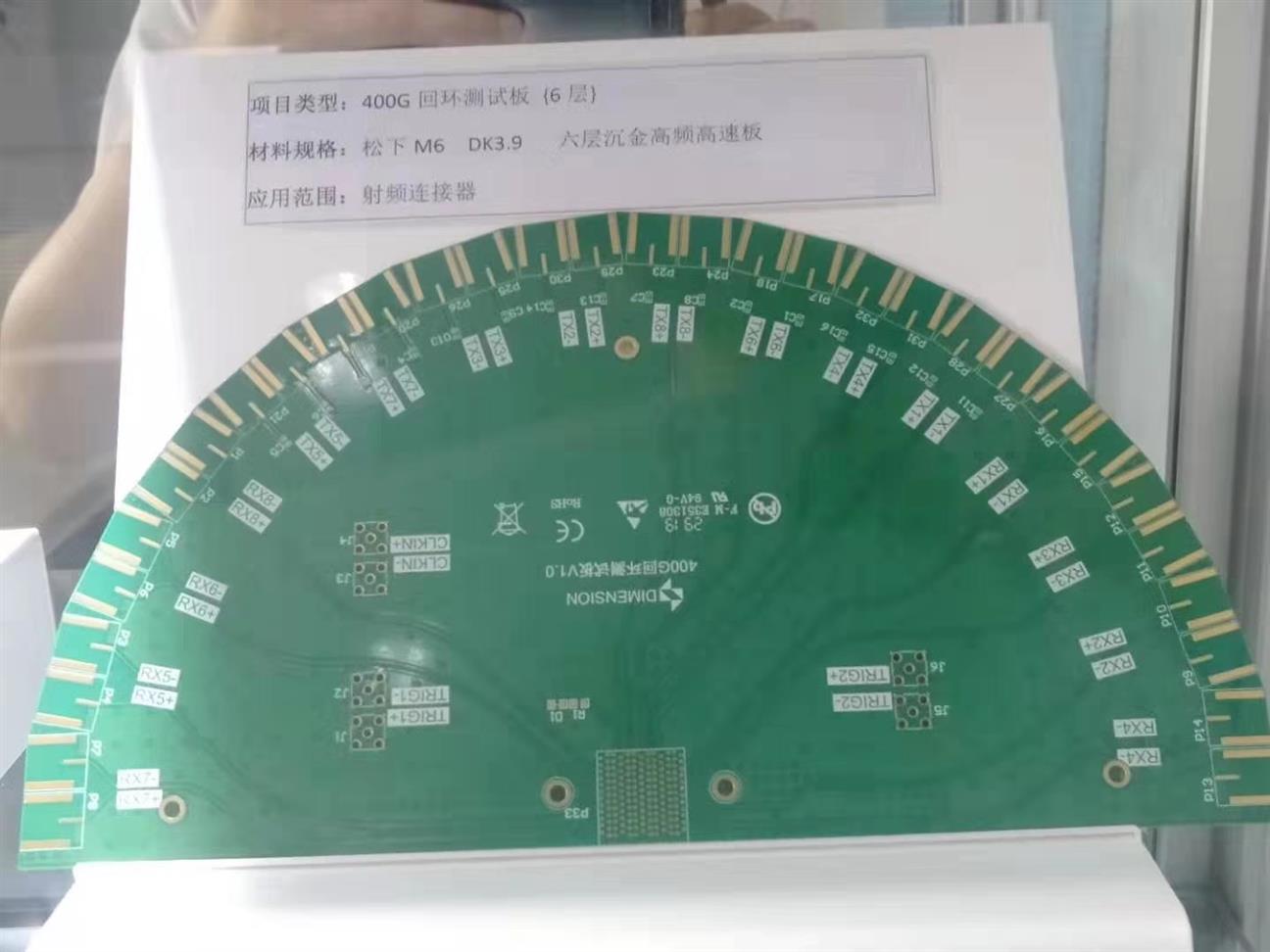

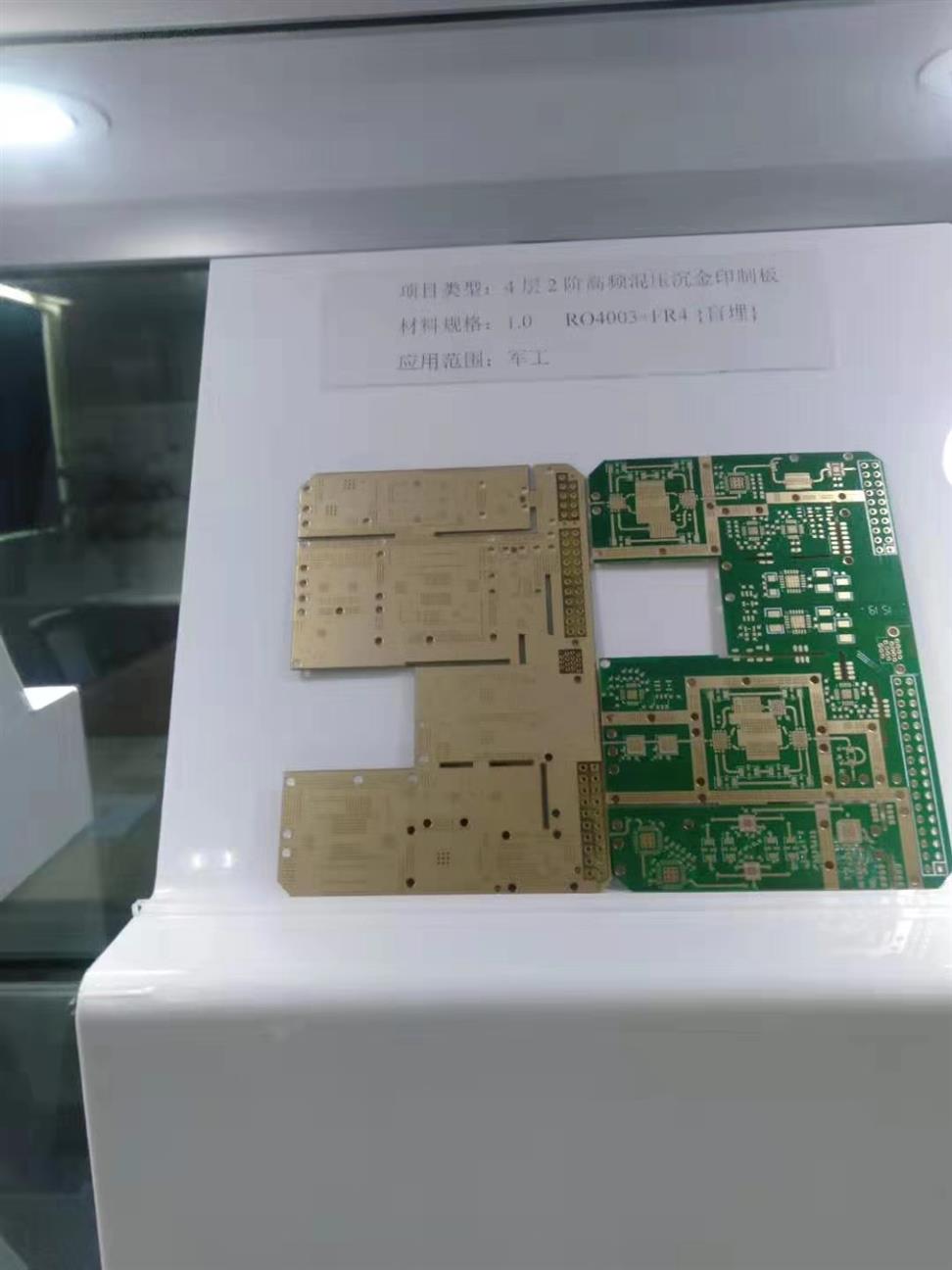

为什么说印刷电路板(PCB)行业即将爆发呢?

主要是PCB的下游受5G,物联网,云计算等需求的爆发,行业景气度呈现出加速的趋势。目前PCB行业发展快速,由此前的应用于家电,台式电脑,笔记本,智能手机到现在的5G,物联网,云计算等运用,可以说已进入了第五个时期。

高速电路PCB的布线设计原则

1.使逻辑扇出小化,只带一个负载。

2.在高速信号线的输出与接收端之间尽可能避免使用通孔,避免引脚图形的十字交叉。尤其是时钟信号线,需要特别注意。

3.上下相邻两层信号线应该互相垂直,避免拐直角弯。

4.并联端接负载电阻应尽可能靠近接收端。

5.为保证小反射,所有的开路线(或没有端接匹配的线)长度必须满足以下式:

Lopen――开长路线度(inches)

trise――信号上升时间(ns)

tpd――线的传播延迟(0.188ns/in――按带线特性)。

6.当开路线长度超过上式要求的值时,应使用串联阻尼电阻器,串联端接电阻应该尽可能地接到输出端的引脚上。

7.保证模拟电路和数字电路分开,AGND和DGND必须通过一个电感或磁珠连接在一起,并尽可能在接近A/D转换器的位置。

8.保证电源的充分去耦。

9.好使用表面安装电阻和电容。