在高速设计中,如何解决信号的完整性问题?

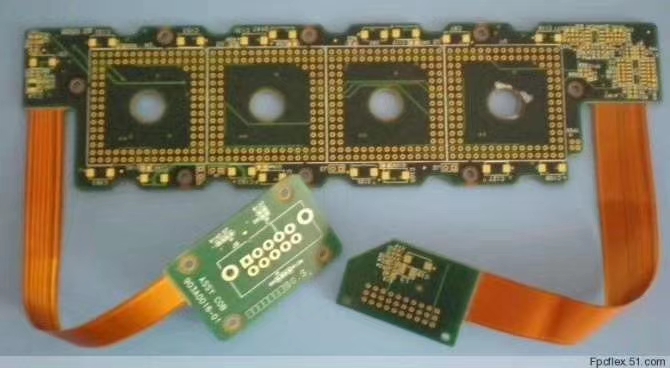

信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(outputimpedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。

为什么说印刷电路板(PCB)行业即将爆发呢?

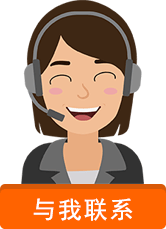

主要是PCB的下游受5G,物联网,云计算等需求的爆发,行业景气度呈现出加速的趋势。目前PCB行业发展快速,由此前的应用于家电,台式电脑,笔记本,智能手机到现在的5G,物联网,云计算等运用,可以说已进入了第五个时期。

近些年来,全球PCB板产能逐渐向东转移,中国,日本,还有亚洲个别国家已成为PCB主要产能贡献国,我国PCB产值也从08年的占世界的31%上升至目前的超过50%。占据了全球的半壁江山。由此,PCB行业下游景气带动PCB发展。

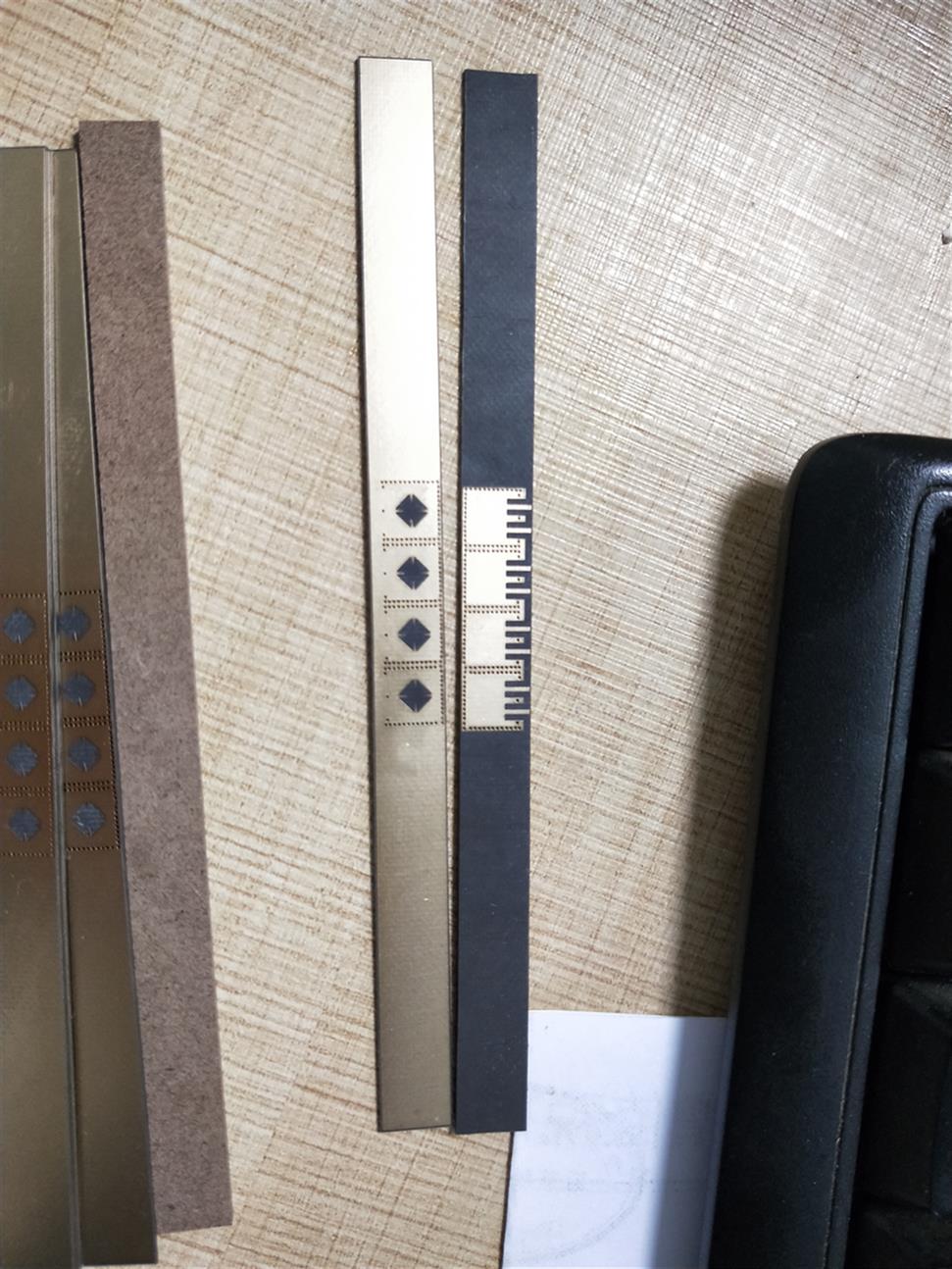

在高速系统中,首先考虑接地和互连线E的传输延迟时间。系统速度受信号线上的传输时间影响很大。虽然集成电路内部处理速度很快,但由于PCB板上普通互连线上的延迟时间较长,导致系统总延迟时间增加,进而导致系统整体速度下降,这一点在高速移位寄存器、同步计数器等步器件尤为明显。因此,如果系统由多块PCB板组成。对于拥有这些特性的高速器件应尽量放在同一个PCB板上,从而避免出现因主PCB板至不同插件板上的时钟信号传渝延迟时间不相等面导致移位寄存器等器件产生移位错误的问题。